HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

Rev. 1.1 — 13 March 2015

**Product data sheet**

### 1. General description

The GreenChip is the latest generation of green Switched Mode Power Supply (SMPS) controller ICs. The TEA1755T combines a controller for Power Factor Correction (PFC) and a flyback controller. Its high level of integration enables cost-effective power supply design using a very low number of external components.

The PFC operates in Quasi-Resonant (QR) or Discontinuous Conduction Mode (DCM), with valley switching.

The specially built-in green functions provide high efficiency at all power levels. At high power levels the flyback operates in QR mode or DCM with valley detection. At medium power levels, the flyback controller switches to Frequency Reduction (FR) mode and limits the peak current to an adjustable minimum value. In low power mode, the PFC switches off to maintain high efficiency. At very low power levels, when the flyback switching frequency drops below 25 kHz, the flyback converter switches to burst mode. During the non-switching phase of burst mode, the internal IC supply current is minimized to further optimize efficiency. Valley switching is used in all operating modes.

The advanced burst mode ensures high-efficiency at low power and good standby power performance while minimizing audible transformer noise.

The TEA1755T is a Multi-Chip Module, (MCM), containing two chips. The proprietary high-voltage BCD800 process makes direct start-up possible from the rectified universal mains voltage in an effective and green way. The second low voltage Silicon-On-Insulator (SOI) is used for accurate, high-speed protection functions and control.

The TEA1755T enables easy design of highly efficient and reliable supplies up to 250 W. These power supply designs are cost-effective, requiring the minimum number of external components.

ELECTRONI

Remark: All values in this document are typical values unless otherwise stated.

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

### 2. Features and benefits

#### 2.1 Distinctive features

- Integrated PFC and flyback controller

- Universal mains supply operation between 70 V (AC) to 276 V (AC)

- Dual-boost PFC with accurate maximum output voltage (NXP Semiconductors patented)

- High level of integration, results in cost-effective designs with very low external component counts

- Adjustable PFC switch off delay

- External PFC switch on and switch off override

- Accurate PFC switch on and switch off control (NXP Semiconductors patent pending)

#### 2.2 Green features

- On-chip start-up current source

- Reduced IC supply current during burst mode enabling ErP lot 6

- Power-down functionality for very low standby power

#### 2.3 PFC green features

- Valley/Zero-Voltage Switching (ZVS) for minimum switching losses (NXP Semiconductors patented)

- Frequency limitation reduces switching losses

- PFC switched off when a low-load is detected at the flyback output

#### 2.4 Flyback green features

- Valley switching for minimum switching losses (NXP Semiconductors patented)

- Frequency reduction with adjustable minimum peak current at low-power operation maintains high-efficiency at low output power levels

- Burst mode operation at very low-power levels for high-efficiency operation

#### 2.5 Protection features

- Safe restart mode for system fault conditions

- Continuous mode protection using demagnetization detection for both converters (NXP Semiconductors patented)

- UnderVoltage Protection (UVP) (foldback during overload)

- Accurate OverVoltage Protection (OVP) for both converters (adjustable for flyback converter)

- Mains voltage independent OverPower Protection (OPP)

- Open control loop protection for both converters. The open-loop protection on the flyback converter is safe restart

- OverTemperature Protection (OTP)

- Low and adjustable OverCurrent Protection (OCP) trip level for both converters

- General-purpose input for latched protection, for use with system OverTemperature Protection (OTP)

TEA1755T

Product data sheet

All information provided in this document is subject to legal disclaimers

© NXP Semiconductors N.V. 2015. All rights reserved.

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

### 3. Applications

The device can be used in all applications requiring an efficient and cost-effective power supply solution for up to 250 W. Notebook adapters in particular benefit from the high level of integration

### 4. Ordering information

| Table 1. Ordering | informatio | n                                                          |          |

|-------------------|------------|------------------------------------------------------------|----------|

| Type number       | Package    |                                                            |          |

| 11                | Name       | Description                                                | Version  |

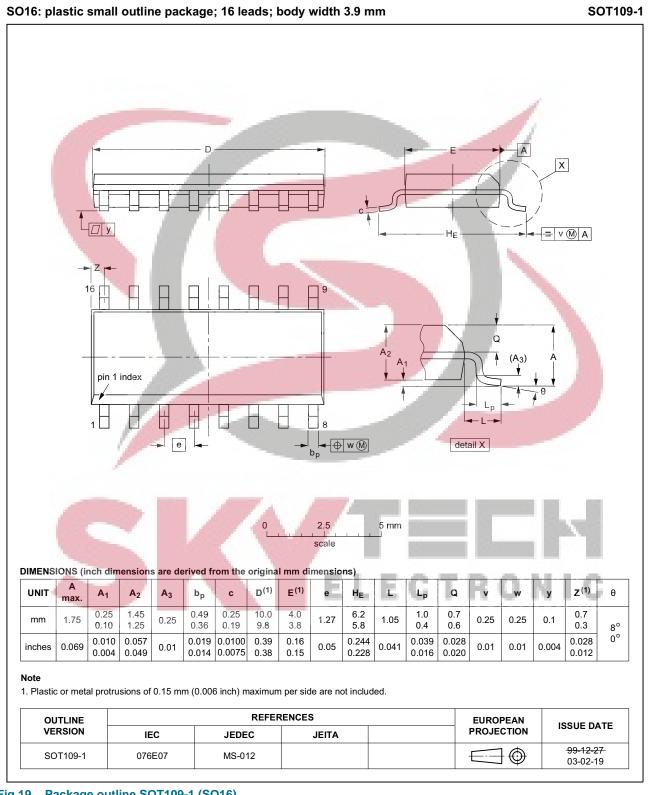

| TEA1755T/1        | SO16       | plastic small outline package; 16 leads; body width 3.9 mm | SOT109-1 |

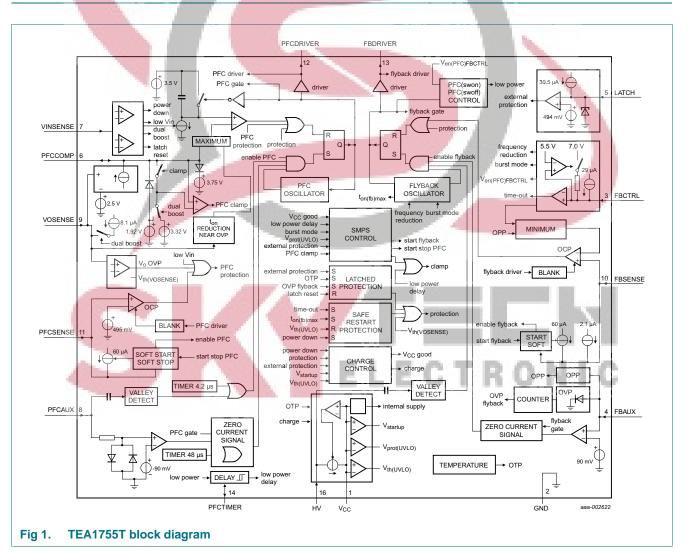

### 5. Block diagram

TEA1755T

All information provided in this document is subject to legal disclaimers

3 of 35

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### **Pinning information** 6.

6.1 Pinning

#### 16 HV V<sub>CC</sub> 1 15 HVS GND 2 FBCTRL 3 14 PFCTIMER FBAUX 4 13 FBDRIVER IC LATCH 5 12 PFCDRIVER 11 PFCSENSE PFCCOMP 6 10 FBSENSE VINSENSE 7 PFCAUX 8 9 VOSENSE aaa-002623 TEA1755T pin configuration (SOT109-1) Fig 2.

#### 6.2 Pin description

|    | Table 2. Pir | n descr | iption                                                             |

|----|--------------|---------|--------------------------------------------------------------------|

|    | Symbol       | Pin     | Description                                                        |

|    | Vcc          | 1       | supply voltage                                                     |

|    | GND          | 2       | ground                                                             |

| 23 | FBCTRL       | 3       | flyback control input                                              |

| 1  | FBAUX        | 4       | auxiliary winding input for demagnetization timing and flyback OVP |

| 1  | LATCH        | 5       | general-purpose protection input                                   |

|    | PFCCOMP      | 6       | PFC frequency compensation                                         |

| -  | VINSENSE     | 7       | mains volta <mark>ge sen</mark> se input                           |

|    | PFCAUX       | 8       | auxiliary winding input for demagnetization timing of the PFC      |

|    | VOSENSE      | 9       | sense input for PFC output voltage                                 |

|    | FBSENSE      | 10      | flyback current sense input                                        |

|    | PFCSENSE     | 11      | PFC current sense input                                            |

|    | PFCDRIVER    | 12      | PFC gate-driver output                                             |

|    | FBDRIVER     | 13      | flyback gate-driver output                                         |

|    | PFCTIMER     | 14      | PFC override and switch off delay timer                            |

|    | HVS          | 15      | high-voltage safety spacer; not connected                          |

|    | HV           | 16      | high-voltage start-up and flyback valley sensing                   |

TEA1755T

### **Product data sheet**

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

### 7. Functional description

#### 7.1 General control

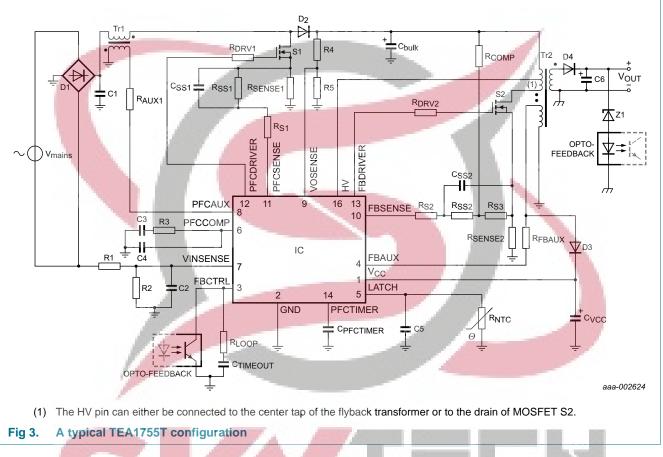

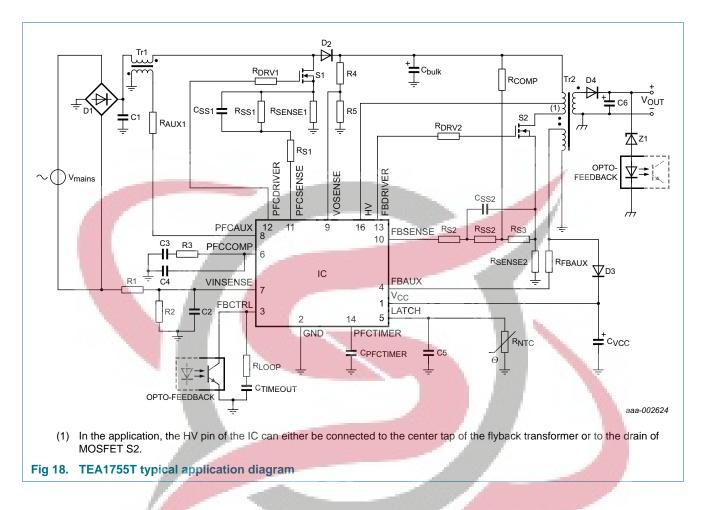

The TEA1755T contains a power factor correction circuit controller and a flyback circuit controller. A typical configuration is shown in <u>Figure 3</u>.

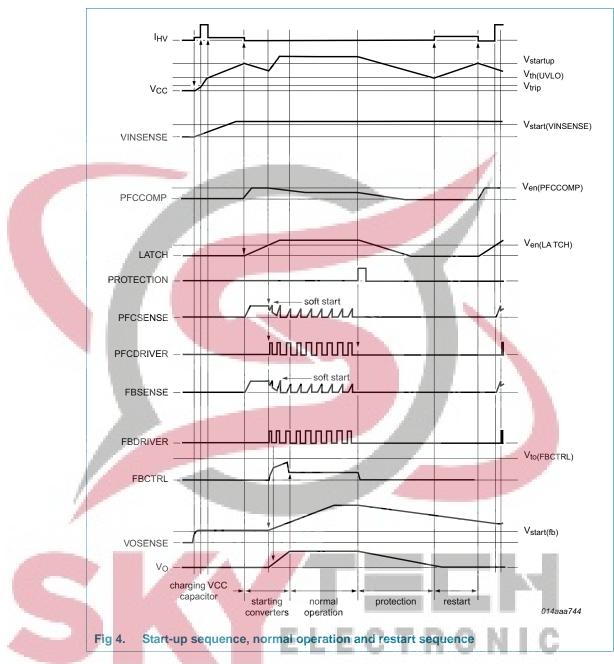

#### 7.1.1 Start-up and UnderVoltage LockOut (UVLO)

Initially, the capacitor on the V<sub>CC</sub> pin is charged from the high-voltage mains using the HV pin.

When  $V_{CC}$  is less than  $V_{trip}$ , the charge current is  $I_{ch(low)}$ . This low current protects the IC if the  $V_{CC}$  pin is shorted to ground. To ensure a short start-up time, the charge current above the  $V_{trip}$  level is increased to  $I_{ch(high)}$ , until  $V_{CC}$  reaches  $V_{th(UVLO)}$ . When  $V_{CC}$  is between  $V_{th(UVLO)}$  and  $V_{startup}$ , the charge current goes low again to ensure a low safe restart duty cycle during fault conditions.

The control logic activates the internal circuitry and switches off the HV charge current when  $V_{CC}$  passes the  $V_{startup}$  level. First, the LATCH pin current source is activated and the soft-start capacitors on the PFCSENSE and FBSENSE pins are charged. Also the clamp circuit on the PFCCOMP pin is activated.

The PFC circuit is activated when the following conditions are met:

TEA1755T Product data sheet All information provided in this document is subject to legal disclaim. Rev. 1.1 — 13 March 2015

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

- the LATCH pin voltage exceeds the V<sub>en(LATCH)</sub> voltage

- the PFCCOMP pin charging current drops below the absolute value of the I<sub>en(PFCCOMP)</sub> current

- the soft-start capacitor on the PFCSENSE pin is charged

The flyback converter is also activated if the soft-start capacitor on the FBSENSE pin is charged. The flyback converter output voltage is then regulated to its nominal output voltage. The auxiliary winding of the flyback converter takes over the IC supply. See Figure 4.

If during start-up, the LATCH pin does not reach the  $V_{en(LATCH)}$  level before  $V_{CC}$  reaches  $V_{th(UVLO)}$ , the LATCH pin output is deactivated. The charge current is switched on again.

When the flyback converter is started,  $V_{FBCTRL}$  is monitored. If the output voltage does not reach its intended regulation level within a specified time,  $V_{FBCTRL}$  reaches the  $V_{to(FBCTRL)}$  level. An error is then assumed and a safe restart is initiated.

When one of the safe restart or latched protection functions are triggered, both converters stop switching and the V<sub>CC</sub> voltage drops to V<sub>th(UVLO)</sub>. A latched protection recharges capacitor C<sub>VCC</sub> using the HV pin, but does not restart the converters. To provide safe restart protection, the capacitor is recharged using the HV pin and the device restarts (see block diagram, Figure 1).

If OVP is triggered on the PFC circuit ( $V_{VOSENSE} > V_{OVP(VOSENSE)}$ ), the PFC controller stops switching until the  $V_{VOSENSE} < V_{OVP(VOSENSE)}$ . If a mains UVP is detected,  $V_{VINSENSE} < V_{stop(VINSENSE)}$ , the PFC controller stops switching until  $V_{VINSENSE} > V_{start(VINSENSE)}$  again.

When the V<sub>CC</sub> pin voltage drops under the UVLO level, both controllers stop switching and enter safe restart mode. In the safe restart mode, the V<sub>CC</sub> pin capacitor is recharged using the HV pin.

At very low burst mode repetition rates,  $V_{CC}$  can drop under the UVLO level. The UVLO protection feature  $V_{prot(UVLO)}$  prevents the decrease when the IC is in burst mode.

#### **NXP Semiconductors**

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.1.2 Power-down mode

The power-down mode can be activated for very low standby power applications by pulling the V<sub>VINSENSE</sub> < V<sub>th(pd)</sub> level. The TEA1755T stops switching and safe restart protection is activated. The high voltage start-up current source is also disabled during power-down and the TEA1755T does not restart until V<sub>VINSENSE</sub> is raised again.

During Power-down mode, all internal circuitry is disabled except for a voltage detection circuit on the VINSENSE pin. This circuit is supplied by the HV pin and draws 12  $\mu A$  from the HV pin for biasing.

TEA1755T Product data sheet

7 of 35

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.1.3 Supply management

All internal reference voltages are derived from a temperature compensated and trimmed on-chip band gap circuit. Internal reference currents are derived from a temperature compensated and trimmed on-chip current reference circuit.

#### 7.1.4 Latch input

The LATCH pin is a general-purpose input pin which is used to switch off both converters. The pin sources a current  $I_{O(LATCH)}$  of 30.5  $\mu$ A. Switching of both converters is stopped when  $V_{LATCH}$  is < 494 mV.

At initial start-up, switching is prevented until the capacitor on the LATCH pin is charged above 582 mV. No internal filtering is performed on this pin. An internal 1.75 V clamp protects the pin from excessive voltages.

#### 7.1.5 Fast latch reset

In a typical application, the mains can be interrupted briefly to reset the latched protection. The bulk capacitor C<sub>bulk</sub> does not have to discharge for this latched protection to reset.

When the VINSENSE voltage drops below 750 mV and is then raised to 860 mV, the latched protection is reset.

The latched protection is also reset by removing both the voltage on the  $V_{CC}$  and HV pins.

#### 7.1.6 Overtemperature protection

An accurate internal temperature protection is provided in the IC. When the junction temperature exceeds the thermal shut-down temperature, the IC stops switching. While OTP is active, the capacitor  $C_{VCC}$  is not recharged from the HV mains. If the  $V_{CC}$  supply voltage is not sufficient, the OTP circuit is supplied from the HV pin.

OTP is a latched protection. It is reset by removing the voltage from both the  $V_{CC}$  and HV pins or by the fast latch reset function (see Section 7.1.5).

#### 7.2 Power factor correction circuit

The Power Factor Correction (PFC) circuit operates in Quasi-Resonant (QR) or Discontinuous Conduction Mode (DCM) with valley switching. The next primary stroke is only started when the previous secondary stroke has ended and the voltage across the PFC MOSFET has reached the minimum value.

V<sub>PFCAUX</sub> is used to detect transformer demagnetization and the minimum voltage across the external PFC MOSFET switch.

#### 7.2.1 ton control (PFCCOMP pin)

The power factor correction circuit is operated in t<sub>on</sub> control. The resulting mains harmonic reduction is well within the class-D requirements.

$V_{PFCCOMP}$  determines the on-time of the PFC. The  $V_{VOSENSE}$  is the transconductance amplifier input which outputs current to the PFCCOMP pin. The regulation  $V_{VOSENSE} = 2.5$  V. The network connected to the PFCCOMP pin and the transconductance amplifier determine the dynamic behavior of the PFC control.

TEA1755T Product data sheet All information provided in this document is subject to legal disclaimers.

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

Operating near the PFC OVP level causes the PFC stage on-time to decrease rapidly to zero.

To reduce the response time, in case of load variation, the PFCCOMP pin is clamped to a minimum level of 2 V during PFC operation. Clamping prevents the on-time increasing too much and improves the PFC response time when the load decreases again.

#### 7.2.2 Valley switching and demagnetization (PFCAUX pin)

The PFC MOSFET is switched on after the transformer is demagnetized. Internal circuitry connected to the PFCAUX pin detects the end of the secondary stroke. It also detects the voltage across the PFC MOSFET. To reduce switching losses and ElectroMagnetic Interference (EMI), the next stroke is started when the voltage across the PFC MOSFET is at its minimum (valley switching).

If a demagnetization signal is not detected on the PFCAUX pin, the controller generates a Zero-Current Signal (ZCS) 48 μs after the last PFC MOSFET gate signal.

If valley signal is not detected on the PFCAUX pin, the controller generates a valley signal 4.2 µs after demagnetization is detected.

To protect the internal circuitry during, for example, lightning events, add a 5 k $\Omega$  series resistor to the PFCAUX pin. To prevent incorrect switching due to external interference, place the resistor close to the IC on the PCB.

#### 7.2.3 Frequency limitation

To optimize the transformer and minimize switching losses, the switching frequency is limited to  $f_{sw(PFC)max}$ . If the frequency for quasi-resonant operation is above the  $f_{sw(PFC)max}$  limit, the system switches to DCM. The PFC MOSFET is only switched on at a minimum voltage across the switch (valley switching).

#### 7.2.4 Mains voltage compensation (VINSENSE pin)

The equation for the transfer function of a power factor corrector contains the square of the mains input voltage. In a typical application, this results in a low bandwidth for low mains input voltages. At high mains input voltages, the Mains Harmonic Reduction (MHR) requirements are hard to meet.

To compensate for the influence of the mains input voltage, the TEA1755T contains a correction circuit. The average input voltage is measured using the VINSENSE pin and the information is fed to an internal compensation circuit. Using this compensation, it is possible to keep the regulation loop bandwidth constant over the mains input range. This feature gives a fast transient response on load steps while still complying with class-D MHR requirements.

In a typical application, a resistor and two capacitors connected to the PFCCOMP pin set the regulation loop bandwidth.

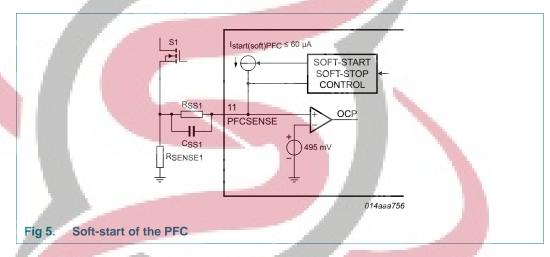

#### 7.2.5 Soft-start (PFCSENSE pin)

To prevent audible transformer noise at start-up or during hiccup, the soft-start function slowly increases the transformer peak current. Place a capacitor  $C_{SS1}$  in parallel with resistor  $R_{SS1}$  (see <u>Figure 5</u>) to implement a soft-start function. An internal current source charges the capacitor to:

TEA1755T Product data sheet All information provided in this document is subject to legal disclaimers.

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

TEA1755T

$$V_{PFCSENSE} = I_{start(soft)PFC} \times R_{SS1}$$

<sup>(1)</sup>

The voltage is limited to V<sub>start(soft)PFC</sub>.

The start level and time constant of the increasing primary current level is externally adjusted by changing the R<sub>SS1</sub> and C<sub>SS1</sub> values.

$$\tau soft-start = 3 \times R_{SSI} \times C_{SSI} \tag{2}$$

The charging current I<sub>start(soft)PFC</sub> flows while the PFCSENSE pin voltage is < 0.5 V. If VPECSENSE exceeds 0.5 V, the soft-start current source starts limiting current Istart(soft)PEC-When the PFC starts switching, the Istart(soft)PFC current source is switched off; see Figure 5.

#### 7.2.6 PFC switch on/switch off control

When the flyback converter output power (see Section 7.3) is low, the flyback converter switches to FR mode. When the switching frequency of the flyback in

FR mode < f<sub>sw(fb)swoff(PFC)</sub> (53 kHz), the PFC circuit is switched off to maintain high efficiency. Connect a capacitor to the PFCTIMER pin (see Section 7.2.7) to delay the PFC switching off.

During low-power mode operation, the PFCCOMP pin is clamped to a minimum voltage of 3.32 V or 1.92 V and a maximum voltage of 3.75 V. The lower clamp voltage depends on VVINSENSE. This voltage limits the maximum power that is delivered when the PFC is switched on again. The upper clamp voltage ensures that the PFC returns from low-power mode to its normal regulation point in a limited time.

In FR mode, when the flyback converter switching frequency exceeds fsw(fb)swon(PFC) (73 kHz), the PFC circuit is switched on. If the flyback converter duty cycle is > 50 % or  $V_{FBCTRL}$  is > 3.75 V, the PFC circuit is also switched on.

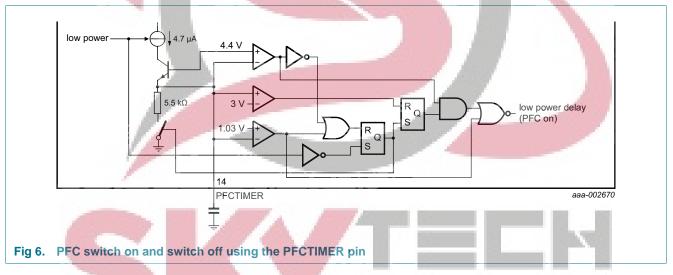

#### 7.2.7 PFC switch off delay (PFCTIMER pin)

When the flyback converter switching frequency in FR mode is < f<sub>sw(fb)swoff(PFC)</sub> (53 kHz), the IC then outputs a 4.7  $\mu$ A current to the PFCTIMER pin. When V<sub>PFCTIMER</sub> reaches 3 V, the PFC is switched off by performing a soft-stop.

TEA1755T Product data sheet

All information provided in this document is subject to legal disclaimers.

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

A switch discharges the PFCTIMER pin capacitor when the flyback controller operating frequency is >  $f_{sw(fb)swon(PFC)}$  (73 kHz). At the same moment, the PFC stage is also switched on.

Connect a capacitor to the PFCTIMER pin (see <u>Section 7.2.7</u>) to prevent the PFC from switching off due to a dynamic load that leads to repetitive crossing of  $f_{sw(fb)swoff(PFC)}$  and  $f_{sw(fb)swon(PFC)}$ . A 1 nF minimum capacitor value is recommended to prevent noise influencing the PFC switch on/ switch off behavior.

The PFCTIMER pin capacitor is also discharged when the flyback maximum switching frequency is higher than 53 kHz. This feature prevents PFC on/off toggling during dynamic loads causing the flyback to operate repetitively near  $f_{sw(fb)swoff(PFC)}$  and  $f_{sw(fb)swon(PFC)}$ .

It is also possible to control PFC switch-on and switch off externally. When V<sub>PFCTIMER</sub> is driven below 1.03 V, the PFC stage is on. When the PFCTIMER pin voltage is driven above 4.4 V, the PFC stage is switched off. The external control overrides the PFC stage control by the flyback controller (see Figure 6).

The PFCTIMER pin has an internal clamp circuit starting around 10 V with a current capability of 0.1 mA

#### 7.2.8 Dual-boost PFC

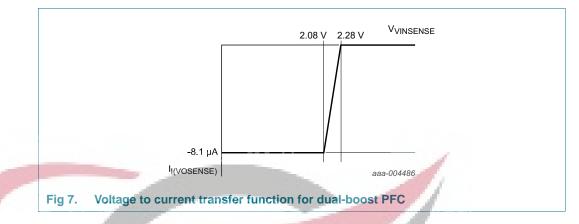

The mains input voltage modulates the PFC output voltage. The mains input voltage is measured using the VINSENSE pin. If  $V_{VINSENSE} < 2.28$  V, the current is sourced from the VOSENSE pin. To ensure switch-over is stable, the current reaches its absolute maximum value for  $V_{VINSENSE} < 2.08$  V, see Figure 7.

At low VINSENSE input voltages, the output current is 8.1  $\mu$ A. This output current, in combination with the resistors on the VOSENSE pin, sets the lower PFC output voltage level at low mains voltages. At high mains input voltages, the current is switched to zero. The PFC output voltage is then at its maximum. As this current is zero in this situation, it does not affect the accuracy of the PFC output voltage.

To ensure a correct switch-off of the application, the VOSENSE current switches to its maximum value of 8.1  $\mu$ A when V<sub>VOSENSE</sub> drops below 2.1 V.

TEA1755T Product data sheet All information provided in this document is subject to legal disclaimers

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.2.9 Overcurrent protection (PFCSENSE pin)

The maximum peak current is limited cycle-by-cycle by sensing the voltage across an external sense resistor, R<sub>SENSE1</sub>, on the source of the external MOSFET. The voltage is measured using the PFCSENSE pin.

#### 7.2.10 Mains undervoltage lockout/brownout protection (VINSENSE pin)

To prevent the PFC from operating at very low mains input voltages,  $V_{VINSENSE}$  is sensed continuously. When  $V_{VINSENSE}$  drops below the  $V_{stop}(VINSENSE)$  level, switching of the PFC is stopped.

#### 7.2.11 Overvoltage protection (VOSENSE pin)

To prevent output overvoltage during load steps and mains transients, an overvoltage protection circuit is built in.

When  $V_{VOSENSE}$  exceeds the  $V_{OVP(VOSENSE)}$  level, switching of the PFC circuit is prevented. Switching of the PFC restarts when the VOSENSE pin voltage drops below the  $V_{OVP(VOSENSE)}$  level again.

OVP is also triggered when the resistor between the VOSENSE pin and ground is open.

#### 7.2.12 PFC open-loop protection (VOSENSE pin)

The PFC circuit does not start switching until the V<sub>VOSENSE</sub> pin is greater than the V<sub>th(ol)</sub>(VOSENSE) level. This feature protects the application from open-loop and VOSENSE short-circuit situations.

#### 7.2.13 Driver (PFCDRIVER pin)

The driver circuit to the gate of the power MOSFET has a current sourcing capability of 500 mA at 2 V on the PFCDRIVER pin and a current sink capability of 1.2 A at 10 V on the PFCDRIVER pin. These capabilities ensure fast switch-on and switch-off of the power MOSFET for efficient operation.

#### 7.3 Flyback controller

The TEA1755T includes a controller for a flyback converter. The flyback converter operates in quasi-resonant, discontinuous conduction mode or burst mode with valley switching. The auxiliary winding of the flyback transformer provides demagnetization detection and powers the IC after start-up.

TEA1755T Product data sheet All information provided in this document is subject to legal disclaimers

Rev. 1.1 — 13 March 2015

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### flyback switching frequency 130 kHz Ipmir adiust frequency reduction 73 kHz discontinuous PFC off PFC on with valley quasi-resonant 53 kHz switching 36.5 kHz 25 kHz burst mode output power aaa-002671 Fig 8. Multimode operation flyback

#### 7.3.1 Multimode operation

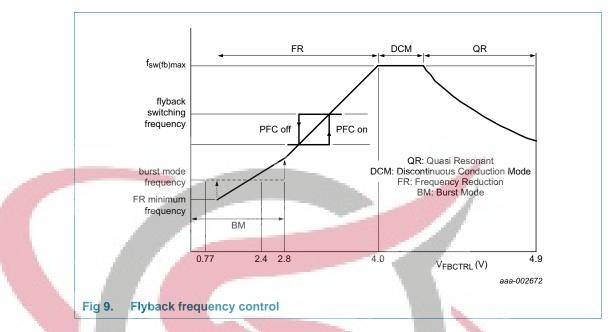

The TEA1755T flyback controller can operate in several modes; see Figure 8.

At high output power the converter switches to quasi-resonant mode. The next converter stroke starts after demagnetization of the transformer and detection of the valley. In quasi-resonant mode switching losses are minimized. This minimization is achieved by the converter only switching on when the voltage across the external MOSFET is at its minimum (see Section 7.3.2).

Valley switching is active in all operating modes.

To prevent high frequency operation at lower loads, the quasi-resonant operation switches to discontinuous mode operation with valley skipping. When the frequency limit is reached, the quasi-resonant operation changes to DCM with valley skipping. The frequency limit reduces the MOSFET switch-on losses and conducted EMI.

At medium power levels, the controller enters Frequency Reduction (FR) mode. A Voltage Controlled Oscillator (VCO) controls the frequency. The minimum frequency in this mode is reduced to approximately 25 kHz. During frequency reduction mode, the primary peak current is kept at an adjustable minimal level to maintain a high efficiency. Valley switching is also active in this mode.

At very low power and standby levels, for which the switching frequency would drop below 25 kHz, the converter enters the burst mode. In burst mode, the switching frequency is 36.5 kHz. The primary peak current is fixed in burst mode.

In frequency reduction mode, the PFC controller switches off as soon as the flyback switching frequency drops below 53 kHz. The flyback maximum frequency changes linearly with the control  $V_{FBCTRL}$  (see Figure 9). Hysteresis is added to ensure a stable PFC switch-on and switch-off. In no-load operation, the switching frequency is reduced to (almost) zero.

#### TEA1755T Product data sheet

13 of 35

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.3.2 Valley switching (HV pin)

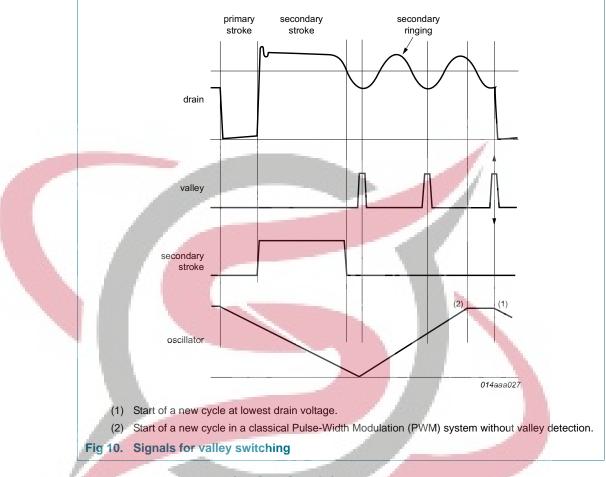

A new cycle starts when the external MOSFET is switched on.  $V_{FBSENSE}$  and  $V_{FBCTRL}$  determine the on-time. The MOSFET is then switched off and the secondary stroke starts (see Figure 10). After the secondary stroke, the drain voltage shows an oscillation with a frequency of approximately:

$$\frac{1}{[2 \times \pi \times \sqrt{(L_p \times C_d)}]}$$

where  $L_p$  is the primary self-inductance of the flyback transformer and  $C_d$  is the capacitance on the drain node.

When the secondary stroke ends and the internal oscillator voltage is high again, the circuit waits for the lowest drain voltage before starting a new primary stroke.

Figure 10 shows the drain voltage, valley signal, secondary stroke signal and the internal oscillator signal.

Valley switching allows high frequency operation because capacitive switching losses are reduced (see Equation 4). High frequency operation makes small and cost-effective magnetic components possible.

$$P = \frac{1}{2} \times C_d \times V^2 \times f \tag{4}$$

TEA1755T Product data sheet (3)

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.3.3 Current mode control (FBSENSE pin)

Current mode control is used for the flyback converter because of its good line regulation.

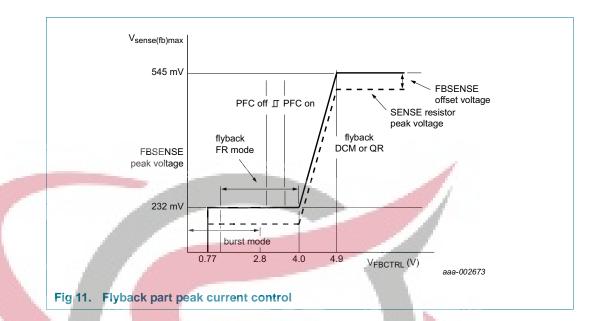

The FBSENSE pin senses the primary current across an external resistor and compares it to an internal control voltage. The internal control voltage is proportional to V<sub>FBCTRL</sub> (see Figure 11).

The FBSENSE pin outputs a current of 2.1  $\mu$ A. This current runs through the resistors from the FBSENSE pin to the sense resistor R<sub>SENSE</sub> and creates an offset voltage. The minimum flyback peak current is adjusted using this offset voltage. Adjusting the minimum peak current level, changes the frequency reduction slope (see Figure 8).

TEA1755T

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.3.4 Demagnetization (FBAUX pin)

The system is always in QR or DCM. The internal oscillator does not start a new primary stroke until the previous secondary stroke has ended.

Demagnetization features a cycle-by-cycle output short-circuit protection by immediately lowering the frequency (longer off-time) and reducing the power level.

Demagnetization recognition is suppressed during the first  $t_{sup(xfmr_ring)}$  time of 2.2 µs. This suppression can be necessary at low output voltages, during start-up and in applications where the transformer has a large leakage inductance.

If the FBAUX pin is open-circuit or not connected, a fault condition is assumed and the converter immediately stops. Operation restarts when the fault condition is removed.

#### 7.3.5 Flyback control/time-out (FBCTRL pin)

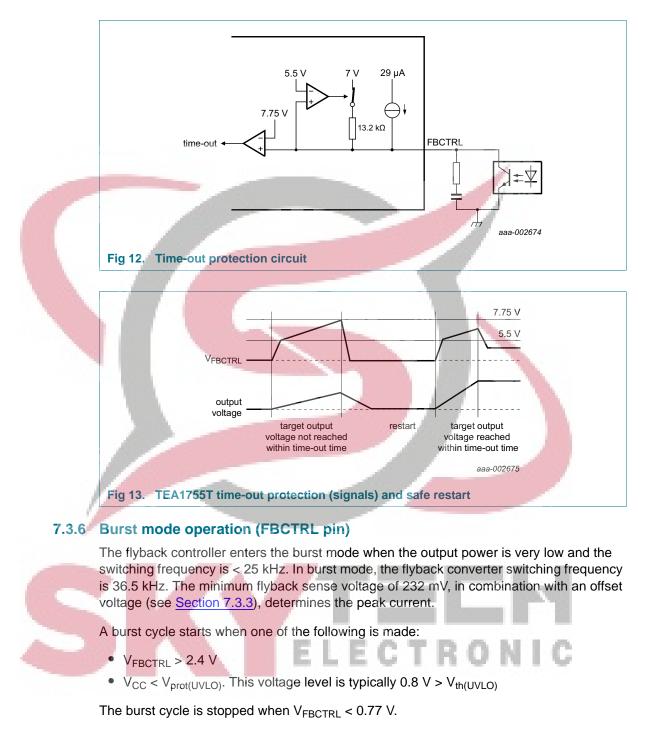

The FBCTRL pin is connected to an internal voltage source of 7 V using an internal 13.2 k $\Omega$  resistor. When V<sub>FBCTRL</sub> > 5.5 V, the resistor is disconnected. The pin is biased with a 29  $\mu$ A current. When V<sub>FBCTRL</sub> > 7.75 V, a fault is assumed, switching is stopped and a restart is made.

If a capacitor and resistor are connected in series to the pin, a time-out function is created which protects against open control loop situations. See Figure 12 and Figure 13. The time-out function is disabled by connecting a resistor (200 k $\Omega$ ) to ground on the FBCTRL pin.

If the pin is short-circuited to ground, switching of the flyback controller is stopped.

Under normal operating conditions, the converter regulates the output voltage.  $V_{FBCTRL}$  varies between 0.77 V at minimum output power and 4.9 V at maximum output power.

TEA1755T Product data sheet

Rev. 1.1 — 13 March 2015

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

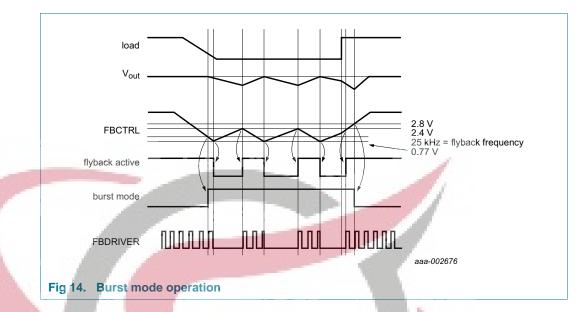

In burst mode, the internal IC supply current is reduced to improve the no-load and low-load input power.

The burst mode is exited and normal operation resumes when the  $V_{FBCTRL} > 2.8 V$  (see Figure 14).

```

TEA1755T

Product data sheet

```

All information provided in this document is subject to legal disclaimers.

17 of 35

### **TEA1755T**

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.3.7 Soft-start (FBSENSE pin)

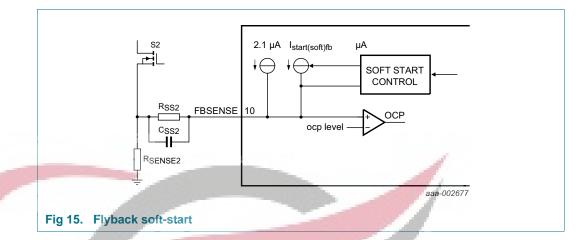

To prevent audible transformer noise during start-up, the soft-start function slowly increases the transformer peak current. Place a capacitor  $C_{SS2}$  in parallel with resistor  $R_{SS2}$  (see Figure 15) to implement the soft-start function.

An internal current source charges the capacitor to:

$$V = I_{start(soft)fb} \times R_{SS2}$$

with a maximum of 0.55 V.

The start level and the time constant of the increasing primary current level can be adjusted externally by changing the values of  $R_{SS2}$  and  $C_{SS2}$ .

$$tsoft-start = 3 \times R_{SS2} \times C_{SS2}$$

The soft-start current I<sub>start(soft)fb</sub> switches on when V<sub>CC</sub> reaches V<sub>startup</sub>. When the V<sub>FBSENSE</sub> reaches 0.55 V, the flyback converter starts switching.

The charging current  $I_{start(soft)fb}$  flows when the  $V_{FBSENSE}$  is < 0.55 V. If  $V_{FBSENSE}$  exceeds 0.55 V, the soft-start current source starts limiting the current. After the flyback converter has started, the soft-start current source is switched off.

When the IC is operating in the burst mode, the soft-start function is switched off.

TEA1755T Product data sheet

(5)

(6)

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.3.8 Maximum on-time

The flyback controller limits the on-time of the external MOSFET to 38.5  $\mu$ s. When the on-time is longer than 38.5  $\mu$ s, the IC stops switching and enters the safe restart state.

#### 7.3.9 Overvoltage protection (FBAUX pin)

An output OVP is implemented in the GreenChip series. In the TEA1755T, the auxiliary voltage is sensed using the current flowing into the FBAUX pin during the secondary stroke. The auxiliary winding voltage is a well-defined replica of the output voltage. An internal filter averages voltage spikes.

An internal up-down counter prevents false OVP detection which can occur during ESD or lightning events. The internal counter counts up by one when the output voltage exceeds the OVP trip level within one switching cycle. The internal counter counts down by two when the output voltage has not exceeded the OVP trip level in one switching cycle. When the counter has reached six, the IC assumes a true overvoltage, sets the latched protection and switches off both converters.

The converter only restarts after the OVP latch is reset. In a typical application, the internal latch is reset when the VINSENSE voltage drops below 750 mV and is then raised to 860 mV. The latched protection is also reset by removing both the  $V_{CC}$  and  $V_{HV}$ .

The demagnetization resistor, R<sub>FBAUX</sub> sets the output voltage V<sub>o(OVP)</sub> at which the OVP function trips:

$$V_{o(OVP)} = \frac{N_s}{N_{aux}} (I_{ovp(FBAUX)} \times R_{FBAUX} + V_{clamp(FBAUX)})$$

(7)

where  $N_s$  is the number of secondary winding and  $N_{aux}$  is the number of auxiliary winding of the transformer. Current  $I_{ovp(FBAUX)}$  is internally trimmed.

Accurate OVP detection is made possible by adjusting the value of  $\mathsf{R}_{\mathsf{FBAUX}}$  to the turns ratio of the transformer.

TEA1755T Product data sheet

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### 7.3.10 Overcurrent protection (FBSENSE pin)

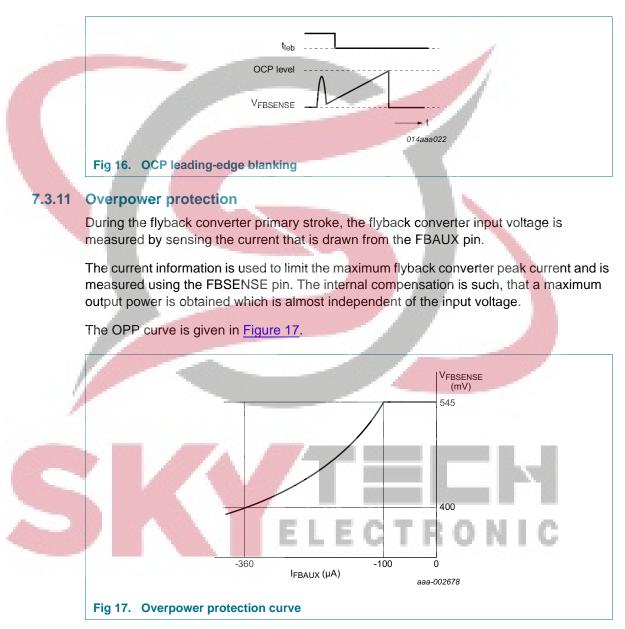

The primary peak current in the transformer is measured accurately cycle-by-cycle using the external sense resistor R<sub>sense2</sub>. The OCP circuit limits V<sub>FBSENSE</sub> to a level set by V<sub>FBCTRL</sub> (see also <u>Section 7.3.3</u>). The OCP detection is suppressed during the leading-edge blanking period, t<sub>leb</sub> (equals  $t_{on(fb)min} - t_{d(FBDRIVER)}$ ), to prevent false triggering due to switch-on spikes.

#### 7.3.12 Driver (FBDRIVER pin)

The driver circuit for the external power MOSFET gate has a current sourcing capability of 500 mA at 2 V on the FBDRIVER pin and a current sink capability of 1.2 A at 10 V on the FBDRIVER pin. These capabilities ensure fast switch-on and switch-off of the power MOSFET for efficient operation.

TEA1755T Product data sheet All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 13 March 2015

20 of 35

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

### 8. Limiting values

#### Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                | Parameter                                         | Conditions                            |     | Min  | Max  | Uni |

|-----------------------|---------------------------------------------------|---------------------------------------|-----|------|------|-----|

| Voltages              |                                                   |                                       |     |      |      |     |

| V <sub>CC</sub>       | supply voltage                                    |                                       |     | -0.4 | +38  | V   |

| VLATCH                | voltage on pin LATCH                              | current limited                       |     | -0.4 | +10  | V   |

| VFBCTRL               | voltage on pin FBCTRL                             |                                       |     | -0.4 | +9   | V   |

| VPFCCOMP              | voltage on pin PFCCOMP                            |                                       |     | -0.4 | +5   | V   |

| VVINSENSE             | voltage on pin VINSENSE                           | current limited                       |     | -0.4 | +10  | V   |

| V <sub>VOSENSE</sub>  | voltage on pin VOSENSE                            | current limited                       | 1   | -0.4 | +10  | V   |

| VPFCAUX               | voltage on pin PFCAUX                             |                                       |     | 25   | +25  | V   |

| V <sub>FBSENSE</sub>  | voltage on pin FBSENSE                            | current limited                       |     | -0.4 | +5   | V   |

| VPFCSENSE             | voltage on pin PFCSENSE                           | current limited                       |     | -0.4 | +5   | V   |

| Vpfctimer             | vol <mark>tage on p</mark> in PFCTIMER            | current limited                       |     | -0.4 | +10  | V   |

| V <sub>HV</sub>       | voltage on pin HV                                 |                                       |     | -0.4 | +650 | V   |

| Currents              |                                                   |                                       |     |      |      |     |

| IFBCTRL               | current on pin FBCTRL                             |                                       |     | -3   | 0    | mA  |

| I <sub>FBAUX</sub>    | current on pin FBAUX                              |                                       |     | -1   | +1   | mA  |

| I <sub>PFCSENSE</sub> | current on pin PFCSENSE                           |                                       |     | -1   | +10  | mA  |

| FBSENSE               | current on pin FBSENSE                            |                                       |     | -1   | +10  | mA  |

| FBDRIVER              | current on pin FBDRIVER                           | δ < 10 %                              |     | -0.8 | +2   | A   |

| IPFCDRIVER            | current on pin PFCDRIVER                          | δ < 10 %                              |     | -0.8 | +2   | A   |

| I <sub>HV</sub>       | current on pin HV                                 | during start-up<br>and restart        |     | -    | 8    | mA  |

|                       |                                                   | $\delta = 3$ % due to dV/dt on HV pin |     | -15  | +30  | mA  |

| General               |                                                   | And Inc.                              | 1   |      |      |     |

| Ptot                  | total power dissipation                           | T <sub>amb</sub> < 75 ℃               |     | -    | 0.6  | W   |

| T <sub>stg</sub>      | storage temperature                               |                                       |     | -55  | +150 | °C  |

| Tj                    | junction temperature                              |                                       |     | -40  | +155 | °C  |

| ESD                   |                                                   | ECT                                   | D   | O I  | 117  |     |

| V <sub>ESD</sub>      | electrostatic di <mark>schar</mark> ge<br>voltage | human body<br>model                   |     | × 1  |      |     |

|                       |                                                   | pins 1 to 14                          | [1] | -2   | +2   | kV  |

|                       |                                                   | pin 16 (HV)                           | [1] | -2   | +2   | kV  |

|                       |                                                   | charged device<br>model               |     | -500 | +500 | V   |

[1] Equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

TEA1755T

21 of 35

Product data sheet

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

### 9. Thermal characteristics

| Table 4.             | Table 4. Thermal characteristics            |                               |     |      |  |  |  |  |  |  |

|----------------------|---------------------------------------------|-------------------------------|-----|------|--|--|--|--|--|--|

| Symbol               | Parameter                                   | Conditions                    | Тур | Unit |  |  |  |  |  |  |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air; JEDEC test board | 127 | K/W  |  |  |  |  |  |  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    | in free air; JEDEC test board | 36  | K/W  |  |  |  |  |  |  |

### **10. Characteristics**

#### Table 5. Characteristics

$T_{amb} = 25$  °C;  $V_{CC} = 20$  V; all voltages are measured with respect to ground (pin 2); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                  | Parameter                                  | Conditions                                                                                                                        | Min   | Тур                            | Max   | Unit |

|-------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------|-------|------|

| Start-up current        | source (HV pin)                            |                                                                                                                                   | 1     |                                |       |      |

| I <sub>HV</sub>         | current on pin HV                          | V <sub>HV</sub> > 75 V                                                                                                            |       |                                |       |      |

|                         |                                            | V <sub>CC</sub> < V <sub>trip</sub>                                                                                               | 0.9   | 1.1                            | 1.3   | mA   |

|                         |                                            | V <sub>th(UVLO)</sub> < V <sub>CC</sub> < V <sub>startup</sub>                                                                    | 0.8   | 1                              | 1.2   | mA   |

|                         |                                            | $V_{trip} < V_{CC} < V_{th(UVLO)}$                                                                                                | 4     | 5                              | 6     | mA   |

|                         |                                            | with auxiliary supply                                                                                                             | -     | -                              | 1.5   | μA   |

|                         | 100                                        | in Power-down mode; V <sub>C</sub> = 0 V                                                                                          | 5     | 12                             | 25    | μA   |

| V <sub>BR</sub>         | breakdown voltage                          |                                                                                                                                   | 650   | -                              | -     | V    |

| Supply voltage r        | management (V <sub>CC</sub> pin)           |                                                                                                                                   |       |                                |       |      |

| V <sub>trip</sub>       | trip voltage                               |                                                                                                                                   | 0.5   | 0.6                            | 0.7   | V    |

| V <sub>startup</sub>    | start-up voltage                           |                                                                                                                                   | 21.3  | 22.3                           | 23.3  | V    |

| V <sub>th(UVLO)</sub>   | undervoltage lockout<br>threshold voltage  |                                                                                                                                   | 12.4  | 13.4                           | 14.4  | V    |

| V <sub>hys</sub>        | hysteresis voltage                         | V <sub>startup</sub> – V <sub>th(UVLO)</sub>                                                                                      | 8.3   | 8.9                            | 9.5   | V    |

| V <sub>prot(UVLO)</sub> | undervoltage lockout<br>protection voltage |                                                                                                                                   | -     | V <sub>th(UVLO)</sub><br>+ 0.8 | -     | V    |

| I <sub>ch(low)</sub>    | low charging current                       | V <sub>HV</sub> > 75 V                                                                                                            |       |                                |       |      |

|                         |                                            | V <sub>CC</sub> < V <sub>trip</sub>                                                                                               | -1.15 | -1                             | -0.85 | mA   |

|                         |                                            | V <sub>th(UVLO)</sub> < V <sub>CC</sub> < V <sub>startup</sub>                                                                    | -1.05 | -0.9                           | -0.75 | mΑ   |

| I <sub>ch(high)</sub>   | high charging current                      | $V_{HV} > 75 V$ ; $V_{trip} < V_{CC} < V_{th(UVLO)}$                                                                              | -5.8  | -4.9                           | -4    | mΑ   |

| I <sub>CC(oper)</sub>   | operating supply<br>current                | no-load on pins FBDRIVER and<br>PFCDRIVER; $V_{FBCTRL} = 5 V$ ;<br>$f_{FB} = f_{PFC} = 100 \text{ kHz}$ ; $\delta = 30 \%$        | 2.45  | 2.7                            | 2.95  | mA   |

|                         |                                            | IC in burst mode; no-load on pins<br>FBDRIVER and PFCDRIVER;<br>flyback switching; $V_{FBCTRL} = 1.6 V$ ;<br>$V_{PFCSENSE} = 0 V$ | 1.75  | 1.95                           | 2.15  | mA   |

|                         |                                            | IC in burst mode; flyback not<br>switching; $V_{FBCTRL} = 0 V$ ;<br>$V_{PFCSENSE} = 0 V$                                          | 1.24  | 1.35                           | 1.46  | mA   |

| I <sub>CC(prot)</sub>   | protection supply current                  | time-out protection triggered; $V_{HV} = 0 V$                                                                                     | 0.3   | 0.45                           | 0.6   | mA   |

TEA1755T

### **TEA1755T**

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### Table 5. Characteristics ...continued

$T_{amb} = 25 \text{ °C}$ ;  $V_{CC} = 20 \text{ V}$ ; all voltages are measured with respect to ground (pin 2); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                                                  | Parameter                                                | Conditions                                                                                                                                      | Min      | Тур    | Max  | Unit |

|---------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|------|

| I <sub>CC(pd)</sub>                                     | power-down mode<br>supply current                        | IC in power-down mode; $V_{HV} = 0 V$                                                                                                           | 0.3      | 0.45   | 0.6  | mA   |

| Input voltage sensin                                    | ng PFC (VINSENSE pin)                                    |                                                                                                                                                 |          |        |      |      |

| V <sub>stop</sub> (VINSENSE)                            | stop voltage on pin<br>VINSENSE                          |                                                                                                                                                 | 0.8      | 6 0.89 | 0.92 | V    |

| V <sub>start</sub> (VINSENSE)                           | start voltage on pin<br>VINSENSE                         |                                                                                                                                                 | 1.1      | 2 1.16 | 1.20 | V    |

| V <sub>flr</sub>                                        | fast latch reset voltage                                 | active after $V_{th(UVLO)}$ is detected                                                                                                         | 0.6      | 0.75   | 0.9  | V    |

| V <sub>flr(hys)</sub>                                   | hysteresis of fast latch reset voltage                   |                                                                                                                                                 | 60       | 110    | 160  | mV   |

| I <sub>I(VINSENSE)</sub>                                | input current on pin<br>VINSENSE                         | VVINSENSE > V <sub>stop</sub> (VINSENSE) after<br>V <sub>start</sub> (VINSENSE) is detected                                                     | 5        | 20     | 50   | nA   |

| V <sub>bst(dual)</sub>                                  | dual boost voltage                                       | high level                                                                                                                                      | 2.0      | 3 2.28 | 2.48 | V    |

|                                                         |                                                          | low level                                                                                                                                       | 1.8      | 3 2.08 | 2.28 | V    |

|                                                         |                                                          | switch-over region                                                                                                                              | 120      | 200    | 280  | mV   |

| V <sub>th(sel)</sub> clmp                               | clamp select threshold voltage                           | on pin VINSENSE                                                                                                                                 | 1.9      | 2      | 2.1  | V    |

| $V_{th(sel)clmp(hys)}$                                  | clamp select threshold voltage hysteresis                |                                                                                                                                                 | 60       | 100    | 140  | mV   |

| V <sub>th(pd)</sub>                                     | power-down threshold voltage                             |                                                                                                                                                 | 285      | 385    | 485  | mV   |

| V <sub>th(pd)exit</sub>                                 | exit power-down<br>threshold voltage                     | V <sub>CC</sub> = 0 V                                                                                                                           | 335      | 460    | 585  | mV   |

| V <sub>hys(pd)</sub>                                    | po <mark>wer-d</mark> own<br>hysteresis voltage          |                                                                                                                                                 | 45       | 75     | 105  | mV   |

| Loop compensation                                       | PFC (PFCCOMP pin)                                        |                                                                                                                                                 |          |        |      |      |

| 9m                                                      | transconductance                                         | VVOSENSE to IO(PFCCOMP)                                                                                                                         | 57       | 77     | 97   | μA/V |

| I <sub>O(PFCCOMP)</sub>                                 | output current on pin                                    | V <sub>VOSENSE</sub> = 2 V; V <sub>PECCOMP</sub> = 2.75 V                                                                                       | 30       | 37     | 44   | μA   |

|                                                         | PFCCOMP                                                  | V <sub>VOSENSE</sub> = 3.3 V;<br>V <sub>PFCCOMP</sub> = 2.75 V                                                                                  | -10      | 8 –88  | -68  | μA   |

| I <sub>en(PFCCOMP)</sub><br>V <sub>clamp(PFCCOMP)</sub> | enable current on pin<br>PFCCOMP<br>clamp voltage on pin | low-power mode; PFC off; lower                                                                                                                  | -<br>[1] | -55    | IC   | μA   |

|                                                         | PFCCOMP                                                  | clamp voltage.                                                                                                                                  |          |        |      |      |

|                                                         |                                                          | $ \begin{array}{l} \mbox{VINSENSE} \geq V_{th(sel)clmp} + \\ V_{th(sel)clmp(hys)} \mbox{ on pin VINSENSE}; \\ V_{VOSENSE} = 2 \ V \end{array} $ | [2] 3.2  | 3.32   | 3.44 | V    |

|                                                         |                                                          | VINSENSE < V <sub>th(sel)clmp</sub> on pin<br>VINSENSE; V <sub>VOSENSE</sub> = 2 V                                                              | 2 1.8    | 1.92   | 2.04 | V    |

|                                                         |                                                          | upper clamp voltage                                                                                                                             | 3.6      | 3.75   | 3.9  | V    |

|                                                         |                                                          | high-power mode; PFC on;<br>uni-directional source clamp;<br>$I_{PFCCOMP} = -30 \ \mu A;$<br>$V_{VOSENSE} = 2.5 \ V$                            | 1.9      | 2      | 2.1  | V    |

TEA1755T

All information provided in this document is subject to legal disclaimers.

Product data sheet

### **TEA1755T**

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### Table 5. Characteristics ...continued

$T_{amb} = 25 \text{ °C}$ ;  $V_{CC} = 20 \text{ V}$ ; all voltages are measured with respect to ground (pin 2); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                            | Parameter                                       | Conditions                                                                                                             | Min   | Тур  | Max   | Unit |

|-----------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>ton</sub> (PFCCOMP)zero    | zero on-time voltage<br>on pin PFCCOMP          |                                                                                                                        | 3.4   | 3.5  | 3.6   | V    |

| Pulse-width modu                  | lator PFC                                       | · · ·                                                                                                                  |       |      |       |      |

| t <sub>on(PFC)</sub>              | PFC on-time                                     | $V_{VINSENSE} = 3.3 V; V_{VOSENSE} = 2 V;$<br>$V_{PFCCOMP} = V_{clamp(PFCCOMP)}$                                       | 1.8   | 2.8  | 3.8   | μS   |

|                                   |                                                 | $V_{VINSENSE} = 1 V; V_{VOSENSE} = 2 V;$<br>$V_{PFCCOMP} = V_{clamp(PFCCOMP)}$                                         | 17    | 27   | 37    | μS   |

| Output voltage ser                | nsing PFC (VOSENSE pir                          | 1)                                                                                                                     |       | 1    |       | 1    |

| V <sub>th(start)</sub> VOSENSE    | start threshold voltage on pin VOSENSE          | open-loop                                                                                                              | 1.05  | 1.1  | 1.15  | V    |

| V <sub>th(stop)</sub> VOSENSE     | threshold stop voltage<br>on pin VOSENSE        |                                                                                                                        | 0.95  | 1    | 1.05  | V    |

| V <sub>hys(VOSENSE)</sub>         | hysteresis voltage on<br>pin VOSENSE            | Vth(start)VOSENSE - Vth(stop)VOSENSE                                                                                   | 75    | 100  | 125   | mV   |

| V <sub>reg</sub> (VOSENSE)        | regulation voltage on pin VOSENSE               | for I <sub>O(PFCCOMP)</sub> = 0 A                                                                                      | 2.475 | 2.5  | 2.525 | V    |

| V <sub>OVP(VOSENSE)</sub>         |                                                 | $t_{on} = 0 \ \mu s$                                                                                                   | 2.59  | 2.62 | 2.65  | V    |

| I <sub>bst(dual)</sub>            | dual boost current                              | V <sub>VINSENSE</sub> < V <sub>bst(dual)</sub> low-level or<br>V <sub>VOSENSE</sub> < 2.1 V; V <sub>FBCTRL</sub> = 5 V | -9.1  | -8.1 | -7.1  | μA   |

|                                   |                                                 | V <sub>VINSENSE</sub> = 4 V                                                                                            | -50   | -25  | -5    | nA   |

| Overcurrent protect               | ction PFC (PFCSENSE pi                          | in)                                                                                                                    |       |      |       |      |

| V <sub>sense</sub> (PFC)max       | maximum PFC sense voltage                       | $\Delta V/\Delta t = 0 V/s$                                                                                            | 465   | 495  | 525   | mV   |

| t <sub>d(PFCDRIVER)</sub>         | delay time on pin<br>PFCDRIVER                  | VPFCSENSE pulse-stepping 400 mV                                                                                        | -     | 50   | -     | ns   |

| t <sub>leb(PFC)</sub>             | PFC leading edge<br>blanking time               | V <sub>PFCSENSE</sub> = 0.75 V                                                                                         | 230   | 290  | 350   | ns   |

| Iprot(PFCSENSE)                   | protection current on pin PFCSENSE              |                                                                                                                        | -50   | -    | -5    | nA   |

| Soft-start PFC (PF                | CSENSE pin)                                     |                                                                                                                        | 1     |      |       |      |

| I <sub>start(soft)PFC</sub>       | PFC soft start current                          |                                                                                                                        | -73   | -60  | -47   | μA   |

| V <sub>start(soft)</sub> PFC      | PFC soft start voltage                          | enab <mark>ling vo</mark> ltage                                                                                        | 0.45  | 0.5  | 0.55  | V    |

| V <sub>stop(soft)PFC</sub>        | PFC soft stop voltage                           | disabling voltage                                                                                                      | 0.4   | 0.45 | 0.5   | V    |

| Oscillator PFC                    |                                                 |                                                                                                                        |       |      |       |      |

| f <sub>sw(PFC)max</sub>           | maximum PFC switching frequency                 |                                                                                                                        | 119   | 139  | 159   | kHz  |

| t <sub>off(PFC)min</sub>          | minimum PFC off-time                            | secondary stroke                                                                                                       | 1.25  | 1.55 | 1.85  | μS   |

| Valley switching P                | FC (PFCAUX pin)                                 |                                                                                                                        |       |      |       |      |

| $(\Delta V/\Delta t)_{vrec(PFC)}$ | PFC valley recognition voltage change with time |                                                                                                                        | -     | -    | 1.7   | V/µs |

| t <sub>to(vrec)</sub> PFC         | PFC valley recognition time-out time            |                                                                                                                        | 3     | 4.2  | 5.4   | μs   |

TEA1755T

### **TEA1755T**

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### Table 5. Characteristics ...continued

$T_{amb} = 25 \text{ °C}$ ;  $V_{CC} = 20 \text{ V}$ ; all voltages are measured with respect to ground (pin 2); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                         | Parameter                                          | Conditions                                                  | Min           | Тур          | Max           | Unit   |

|--------------------------------|----------------------------------------------------|-------------------------------------------------------------|---------------|--------------|---------------|--------|

| Demagnetization n              | nanagement PFC (PFCA                               | UX pin)                                                     |               |              |               |        |

| V <sub>th(comp)</sub> PFCAUX   | comparator threshold<br>voltage on pin<br>PFCAUX   |                                                             | -125          | -90          | -55           | mV     |

| t <sub>to(demag)</sub> PFC     | PFC demagnetization time-out time                  |                                                             | 39            | 48           | 57            | μS     |

| Iprot(PFCAUX)                  | protection current on<br>pin PFCAUX                | V <sub>PFCAUX</sub> = 50 mV                                 | -75           | 1            | -5            | nA     |

| PFC off delay (PFC             | TIMER pin)                                         |                                                             | 1             |              |               |        |

| I <sub>source</sub> (PFCTIMER) | source current on pin<br>PFCTIMER                  | V <sub>PFCTIMER</sub> = 2.5 V                               | -5.4          | -4.7         | -4            | μA     |

| R <sub>sink(PFCTIMER)</sub>    | sink resistance on pin<br>PFCTIMER                 | V <sub>PFCTIMER</sub> = 2.5 V                               | 4             | 5.5          | 7             | kΩ     |

| V <sub>start(PFCTIMER)</sub>   | start voltage on pin<br>PFCTIMER                   |                                                             | 0.93          | 1.03         | 1.13          | V      |

| V <sub>stop</sub> (PFCTIMER)   | stop voltage on pin<br>PFCTIMER                    |                                                             | 2.85          | 3            | 3.15          | V      |

| V <sub>th(off)</sub> PFCTIMER  | switch-off threshold<br>voltage on pin<br>PFCTIMER | PFC override voltage                                        | 4.2           | 4.4          | 4.6           | V      |

| Driver (PFCDRIVE               | R pin)                                             |                                                             |               |              |               |        |

| I <sub>src(PFCDRIVER)</sub>    | source current on pin<br>PFCDRIVER                 | V <sub>PFCDRIVER</sub> = 2 V                                | 4             | -0.5         | -             | A      |

| Isink(PFCDRIVER)               | sink current on pin<br>PFCDRIVER                   | V <sub>PFCDRIVER</sub> = 2.5 V                              | -             | 0.7          | -             | A      |

| V <sub>O</sub> (PFCDRIVER)max  | maximum output<br>voltage on pin<br>PFCDRIVER      |                                                             | 10            | 11           | 12            | V      |

| OverVoltage Protect            | ction flyback (FBAUX pir                           | 1)                                                          |               |              | 1.5           |        |

| I <sub>ovp(FBAUX)</sub>        | overvoltage protection<br>current on pin FBAUX     |                                                             | 279           | 300          | 321           | μΑ     |

| Demagnetization m              | nanagement flyback (FB                             | AUX pin)                                                    |               |              |               |        |

| V <sub>th(comp</sub> )FBAUX    | comparator threshold voltage on pin FBAUX          | ELECT                                                       | 60            | 90           | 120           | mV     |

| Iprot(FBAUX)                   | protection current on<br>pin FBAUX                 | V <sub>FBAUX</sub> = 50 mV                                  | -65           | -            | -5            | nA     |

| V <sub>clamp(FBAUX)</sub>      | clamp voltage on pin<br>FBAUX                      | I <sub>FBAUX</sub> = -100 μA<br>I <sub>FBAUX</sub> = 300 μA | -0.75<br>0.87 | -0.7<br>0.92 | -0.65<br>0.97 | V<br>V |

| t <sub>sup(xfmr_ring)</sub>    | transformer ringing suppression time               |                                                             | 1.7           | 2.2          | 2.7           | μS     |

| Pulse width modul              | ••                                                 | 1                                                           |               |              | 1             |        |

| t <sub>on(fb)max</sub>         | maximum flyback<br>on-time                         |                                                             | 32.5          | 38.5         | 44.5          | μS     |

TEA1755T

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### Table 5. Characteristics ...continued

$T_{amb} = 25 \text{ °C}$ ;  $V_{CC} = 20 \text{ V}$ ; all voltages are measured with respect to ground (pin 2); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                        | Parameter                                                          | Conditions                                                         | Min   | Тур   | Max   | Unit |

|-------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|------|

| Oscillator flyback            |                                                                    |                                                                    |       | 1     |       |      |

| f <sub>sw(fb)max</sub>        | maximum flyback<br>switching frequency                             |                                                                    | 110   | 130   | 150   | kHz  |

| V <sub>start(red)f</sub>      | frequency reduction<br>start voltage                               | transfer from DCM/QR to FR mode                                    | 3.8   | 4     | 4.2   | V    |

| f <sub>sw(fb)swon(PFC)</sub>  | PFC switch-on flyback<br>switching frequency                       |                                                                    | 70    | 73    | 76    | kHz  |

| f <sub>sw(fb)swoff(PFC)</sub> | PFC switch-off flyback switching frequency                         |                                                                    | 50    | 53    | 56    | kHz  |

| f <sub>sw(fb)burst(ent)</sub> | enter burst mode<br>flyback switching<br>frequency                 | enter burst mode                                                   | 21    | 25    | 29    | kHz  |

| f <sub>sw(fb)burst</sub>      | burst mode flyback<br>switching frequency                          | normal operation                                                   | 31    | 36.5  | 42    | kHz  |

| Ven(PFC)FBCTRL                | PFC enable voltage<br>on pin FBCTRL                                | override voltage                                                   | 3.4   | 3.75  | 4.1   | V    |

| Peak current contro           | I flyback (FBCTRL pin)                                             |                                                                    |       |       | 1     |      |

| V <sub>FBCTRL</sub>           | voltage on pin<br>FBCTRL                                           | for maximum flyback peak current                                   | 4.6   | 4.9   | 5.2   | V    |

| V <sub>to(FBCTRL)</sub>       | time-out voltage on                                                | enable voltage                                                     | 5.3   | 5.5   | 5.7   | V    |

|                               | pin FBCTRL                                                         | trip voltage                                                       | 7.3   | 7.75  | 8.2   | V    |

| V <sub>th(burst)off</sub>     | off-state burst mode<br>threshold voltage                          | on pin FBCTRL                                                      | 0.62  | 0.77  | 0.92  | V    |

| V <sub>th(burst)on</sub>      | on-state burst mode<br>threshold voltage                           | on pin FBCTRL                                                      | 2.2   | 2.4   | 2.6   | V    |

| V <sub>th(burst)exit</sub>    | exit burst mode<br>threshold voltage                               | on pin FBCTRL                                                      | 2.6   | 2.8   | 3     | V    |

| Vburst(exit-on)               | burst mode voltage<br>difference between<br>exit and on-state      | pin FBCTRL = V <sub>th(burst)exit</sub> - V <sub>th(burst)on</sub> | 325   | 390   | 455   | mV   |

| V <sub>burst(on-off)</sub>    | burst mode voltage<br>difference between<br>on-state and off-state | pin FBCTRL = V <sub>th(burst)on</sub> - V <sub>th(burst)off</sub>  | 1.5   | 1.63  | 1.76  | V    |

| R <sub>int(FBCTRL)</sub>      | internal resistance on<br>pin FBCTRL                               |                                                                    | 9.8   | 13.2  | 16.5  | kΩ   |

| I <sub>O(FBCTRL)</sub>        | output current on pin                                              | V <sub>FBCTRL</sub> = 0 V                                          | -0.75 | -0.6  | -0.45 | mA   |

|                               | FBCTRL                                                             | V <sub>FBCTRL</sub> = 4.5 V                                        | -0.3  | -0.24 | -0.18 | mA   |

| I <sub>to(FBCTRL)</sub>       | time-out current on pin<br>FBCTRL                                  | V <sub>FBCTRL</sub> = 6 V                                          | -35   | -29   | -23   | μA   |

Product data sheet

### **TEA1755T**

### HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

#### Table 5. Characteristics ...continued

$T_{amb} = 25 \text{ °C}$ ;  $V_{CC} = 20 \text{ V}$ ; all voltages are measured with respect to ground (pin 2); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                           | Parameter                                                 | Conditions                                                                     | Mir            | п Тур     | Max           | Unit |

|----------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|----------------|-----------|---------------|------|

| Valley switching fl              | yback (HV pin)                                            | ·                                                                              |                |           |               |      |

| $(\Delta V/\Delta t)_{vrec(fb)}$ | flyback valley<br>recognition voltage<br>change with time |                                                                                | <u>[3]</u> –75 | ; -       | +75           | V/µs |

| t <sub>d(vrec-swon)</sub>        | valley recognition to switch-on delay time                |                                                                                | <u>[3]</u> -   | 75        | -             | ns   |

| Soft-start flyback (             | FBSENSE pin)                                              |                                                                                |                | 1         |               |      |

| Istart(soft)fb                   | flyback soft start<br>current                             |                                                                                | -75            | -60       | -45           | μA   |

| V <sub>start(soft)fb</sub>       | flyback soft start<br>voltage                             | enable voltage                                                                 | 0.5            | 0.55      | 0.6           | V    |

| OverCurrent prote                | ction flyback (FBSENSE                                    | pin)                                                                           |                |           |               | -    |

| V <sub>sense(fb)max</sub>        | maximum flyback<br>sense voltage                          | $\Delta V/\Delta t = 0 V/s$                                                    | 525            | 545       | 565           | mV   |

| Vsense(fb)min                    | minimum flyback<br>sense voltage                          | $\Delta V/\Delta t = 0 V/s$                                                    | 221            | 232       | 243           | mV   |

| t <sub>d(FBDRIVER)</sub>         | delay time on pin<br>FBDRIVER                             | V <sub>FBSENSE</sub> pulse-stepping 400 mV<br>around V <sub>sense(fb)max</sub> | ·              | 80        |               | ns   |

| t <sub>on(fb)min</sub>           | minimum flyback<br>on-time                                | V <sub>FBCRTL</sub> = 3 V; V <sub>FBSENSE</sub> = 0.75 V                       | 280            | ) 340     | 400           | ns   |